# Comparing Bus Solutions

F. Alicke; F. Bartholdy; S. Blozis; F. Dehmelt; P. Forstner; N. Holland;

MSLP Europe

J. Huchzermeier

#### **ABSTRACT**

This report is intended to be a reference tool for finding the most appropriate bus interface solution for today's advanced system architecture.

This paper focuses on bus interface solutions for different backplane applications. It gives an overview of the different bus solutions available from Texas Instruments (TI<sup>TM</sup>).

Today, advanced bus systems designers have a problem: many different solutions can be used to solve the same problem. The task for the designers is to figure out the optimum solution for their special application.

In order to ease this choice, this application report has been created. The different key parameters are composed in a way that developers may easily find the optimum bus solution for their systems.

The report is split into product family sections to allow easy distinction between various solutions. Each family-section of this report covers details on the electrical parameters and appropriate protocols, as well as application and feature-benefit information on the chosen product family.

All sections are set up in the same order, such that fast comparison and selection of the most appropriate solution is possible.

Keywords: ABT, AHC, BTL, CompactPCI™, FlatLink™, Gigabit, GTL, IEEE1284, IEEE1394, USB, LVDM, LVDS, LVT, PCI, TIA/EIA-232-F (RS-232), TIA/EIA-422-B (RS-422), TIA/EIA-485-A (RS-485), and TIA/EIA-644, SCSI, SERDES, SSTL, GTLP, GTL+, ALVT, FB+, ABTE.

## Contents

| Overview                                                      | . 7 |

|---------------------------------------------------------------|-----|

| Single-Ended Versus Differential Data Transmission            | 10  |

| Single-Ended Transmission                                     | 10  |

| Advantages of Single-Ended Transmission                       | 10  |

| Disadvantages of Single-Ended Transmission                    | 11  |

| Differential Transmission                                     | 12  |

| Advantages of Differential Transmission                       | 12  |

| Disadvantages of Differential Transmission                    | 12  |

| Standard Switching Levels                                     | 13  |

| Interconnectivity                                             | 15  |

| Parallel Versus Serial Transmission                           | 16  |

| Advantages of Parallel Transmission                           | 16  |

| Advantages of Serial Transmission                             | 16  |

| Various Widely Used Data Transmission Topologies              | 17  |

| IEEE 1394 Cable and Backplane Applications (FireWire)         | 18  |

| Electrical                                                    | 18  |

| Protocol                                                      |     |

| Applicability and Typical Application for IEEE 1394           |     |

| Applicability and Typical Application for IEEE 1394 Backplane |     |

| Features                                                      |     |

| Universal Serial Bus (USB)                                    |     |

| Electrical                                                    |     |

| Protocol                                                      |     |

| Applicability and Typical Applications                        |     |

| Features                                                      |     |

| TIA/EIA-232                                                   |     |

| Electrical                                                    |     |

| Protocol                                                      |     |

| Features                                                      |     |

| TIA/EIA-422                                                   |     |

| Electrical                                                    |     |

| Protocol                                                      |     |

| Applicability                                                 |     |

| Features                                                      |     |

| TIA/EIA-485                                                   | 28  |

| Electrical                                                    | 28  |

| Protocol                                                      | 28  |

| Applicability                                                 | 28  |

| Features                                                      | 28  |

| SCSI                                                          |     |

| Electrical                                                    | _   |

| Protocol                                                      |     |

| Applicability and Typical Application                         |     |

| Features                                                      | 30  |

| TIA/EIA-644 (LVDS)                                   | 31 |

|------------------------------------------------------|----|

| Electrical                                           | 31 |

| Protocol                                             | 32 |

| Applicability                                        | 32 |

| Features                                             | 32 |

| LVDM                                                 |    |

| Electrical                                           |    |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             |    |

| LVDS Serdes and FlatLink                             |    |

| Electrical                                           |    |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             |    |

|                                                      |    |

| Serial Gigabit CMOS                                  |    |

| Electrical                                           | _  |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             |    |

| PCI/CompactPCI                                       |    |

| Electrical                                           |    |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             | 44 |

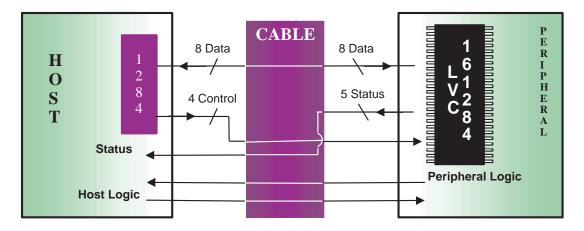

| IEEE 1284 Compatible Devices (SN74yyy1284)           | 45 |

| Electrical                                           | 45 |

| Protocol                                             | 45 |

| Applicability                                        | 45 |

| Features                                             | 46 |

| General-Purpose Interface Logic at 5-V and 3.3-V     | 47 |

| Electrical                                           |    |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             |    |

| Backplane Transceiver Logic (SN74FBxxx)              |    |

| Electrical                                           |    |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             |    |

|                                                      |    |

| Gunning Transceiver Logic (SN74GTLxxx) – SN74GTL1655 |    |

| Electrical                                           |    |

| Protocol                                             |    |

| Applicability                                        |    |

| Features                                             | 54 |

| Gunning Transceiver Logic Plus (SN74GTLPxxx) | 55 |

|----------------------------------------------|----|

| Electrical                                   |    |

| Protocol                                     |    |

| Applicability                                | 56 |

| Features                                     | 56 |

| Stub Series Terminated Logic (SN74SSTLxxx)   | 58 |

| Electrical                                   |    |

| Protocol                                     |    |

| Applicability                                |    |

| Features                                     |    |

| Summary                                      | 61 |

| References                                   |    |

| Glossary                                     | 63 |

| TI Contact Numbers                           |    |

# **List of Figures**

| 1  | Signaling Rate Versus Cable Length                                               | 7    |

|----|----------------------------------------------------------------------------------|------|

| 2  | Single-Ended Transmission With Parallel Termination at Line End                  | . 10 |

|    | Differential Transmission                                                        |      |

| 4  | Switching Levels of Single-Ended Transmission Standards                          | . 13 |

| 5  | Switching Levels of Differential Transmission Standards                          | . 14 |

| 6  | Different Interconnection Scenarios                                              | . 15 |

| 7  | Principle of Parallel and Serial Transmission                                    | . 16 |

| 8  | Point-to-Point Connection                                                        | . 17 |

| 9  | Multi-Drop Connection                                                            | . 17 |

| 10 | Multi-Point Connection Using Multiple Transceiver                                | . 17 |

| 11 | Possible Interconnections Using 1394 as Interface                                | . 20 |

| 12 | Principle Application Setup Using 1394 Interface                                 | . 21 |

| 13 | USB – Tiered Star Topology                                                       | . 24 |

| 14 | Null Modem Application Using RS232                                               | . 25 |

| 15 | Supply Current Versus Switching Frequency                                        | . 31 |

| 16 | Typical Application – FlatLink Used as an Interface in a Notebook                | . 35 |

| 17 | GMII-2 Interface                                                                 | . 37 |

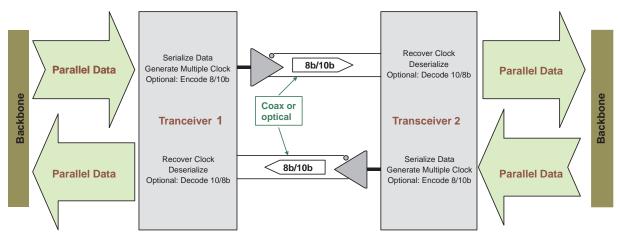

| 18 | Serdes Interface Using Two Transceivers                                          | . 38 |

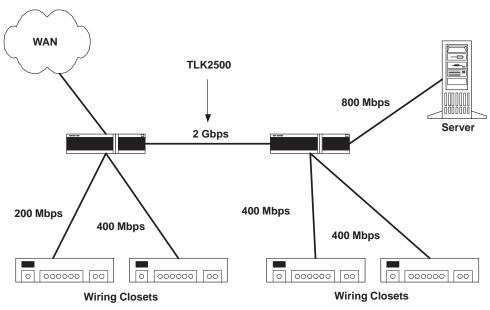

| 19 | High-Speed Interface Using TLK2500                                               | . 39 |

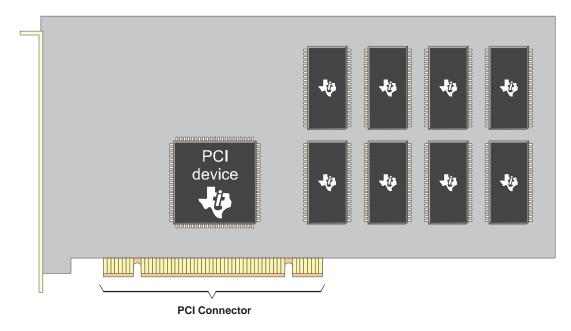

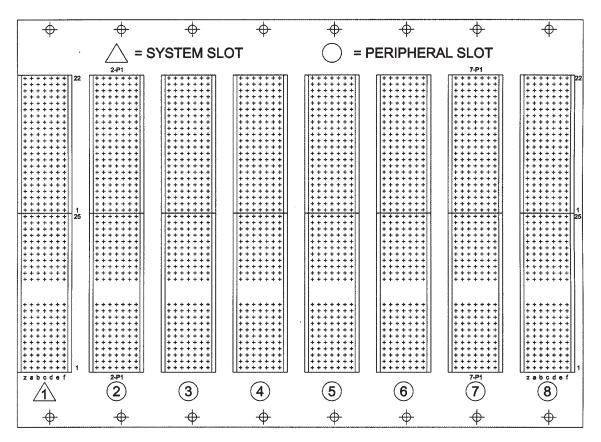

| 20 | PCI Card for Personal Computer                                                   | . 42 |

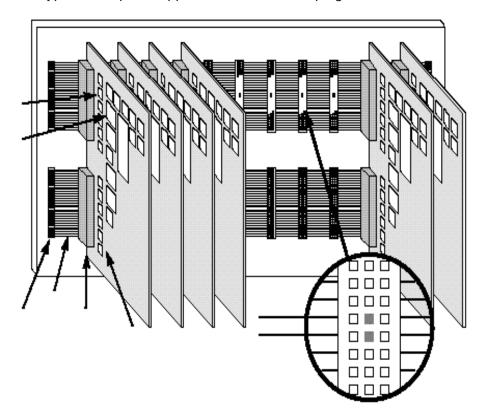

| 21 | CompactPCI Backplane                                                             | . 42 |

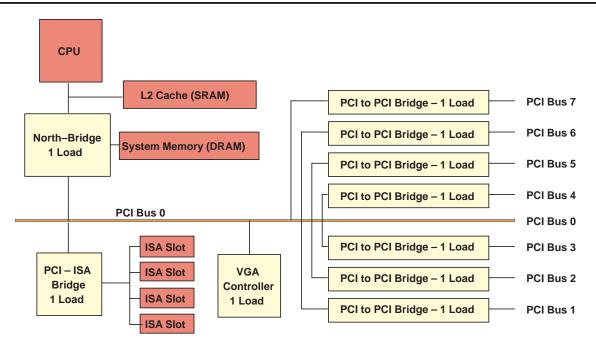

| 22 | PCI Bus System With 8 PCI Buses                                                  | . 43 |

| 23 | Typical Application Showing a 1284 Interface                                     | . 45 |

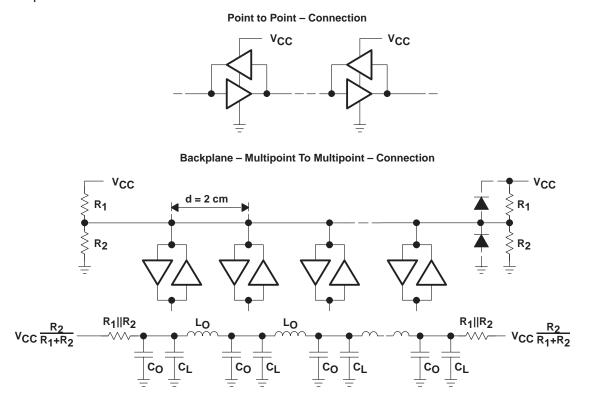

| 24 | Point-to-Point Connection/Backplane Bus With Replacement Circuit – Showing 1 Bit | . 47 |

|    | Typical Backplane Application Using Several Plug-In Cards                        |      |

| 26 | Principle Setup of an Open Collector Bus System Using BTL Devices                | . 51 |

| 27 | Principle Setup of an Open Collector Bus System Using GTL Devices                | . 53 |

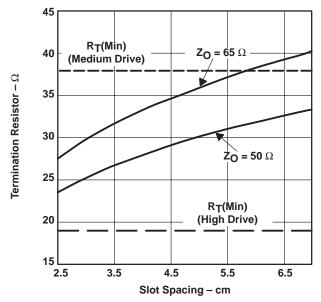

| 28 | RT Versus Slot Spacing With GTLP Medium and High Drive Devices                   | . 55 |

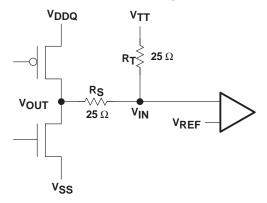

| 29 | Typical Output Buffer Environment, Class II of SSTL Standard                     | . 58 |

| 30 | DDR SDRAM Memory Interfacing Solution Using the SN74SSTL16857                    | . 59 |

## **List of Tables**

| 1  | Bus Interface Selection Guide                               | . 9 |

|----|-------------------------------------------------------------|-----|

| 2  | Top IEEE 1394 Link Layer Device List (PC)                   | 22  |

|    | Top IEEE 1394 Link Layer Device List (Non-PC)               |     |

| 4  | Top IEEE 1394 Physical Layer Device List                    | 22  |

| 5  | Top USB HUB Device List                                     | 24  |

| 6  | Top TIA/EIA-232 Device List                                 | 26  |

| 7  | Top TIA/EIA-422 Device                                      | 27  |

| 8  | Top TIA/EIA-485 Device List                                 | 28  |

| 9  | Top SCSI Device List                                        | 30  |

| 10 | Top LVDS Device List                                        | 32  |

| 11 | Top LVDM Device List                                        | 33  |

| 12 | Typical Multiplexing Ratio for Serdes Devices               | 34  |

| 13 | Top LVDS Serdes Device List                                 | 36  |

| 14 | Top Serial Gigabit Device List                              | 40  |

| 15 | Top Device List – PCI Products                              | 44  |

| 16 | Top Device List – IEEE 1284-Compatible Devices              | 46  |

| 17 | Selected Characteristics for General-Purpose Logic Families | 48  |

| 18 | Top Feature List of Advanced System Logic by Logic Family   | 49  |

| 19 | Top Device List – Backplane Transceiver Logic               | 52  |

| 20 | Top Device List GTL                                         | 54  |

| 21 | Top Device List GTLP                                        | 57  |

| 22 | Top Device List for Stub Series Termination Logic           | 60  |

### Overview

In today's information-hungry society, transmitting data over several inches between computer memory and display screen is just as critical as sending it halfway around the globe. Over the past three decades, Texas Instruments has combined its expertise in high-speed digital and analog technologies. TI is constantly pushing the capabilities and extending the performance parameters of practically every data transmission standard, including TIA/EIA-232, TIA/EIA-423, TIA/EIA-422, TIA/EIA-485, Fibre Channel, electrical characteristics of low voltage differential signaling (LVDS), IEEE 1394 (FireWire™/i.LINK), universal serial bus (USB), GeoPort™ and Infrared Data Association (IrDA).

This application report provides the reader with an overview of the different bus systems available today and should give enough insight into which standard or which bus configuration would suit the customer's needs. Before we discuss each standard, its technical features, and the products that TI offers, it is important to understand the fundamentals behind the different bus configurations available.

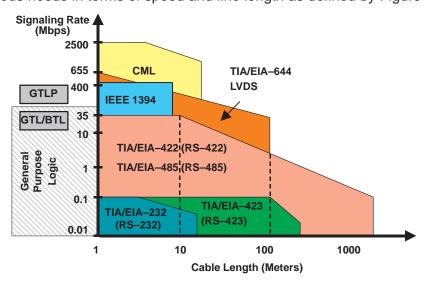

Typically, data transmission, as the name suggests, is a means of moving data from one location to another. In general, there are two main parameters that define how the information is transferred. These parameters are the distance, the space between the sending and the receiving systems and speed, and the rate at which data has to be passed to the receiving device. Different transmission standards, such as TIA/EIA-232, IEEE 1394 and LVDS, provide solutions for various needs in terms of speed and line length as defined by Figure 1.

Figure 1. Signaling Rate Versus Cable Length

It can be seen from Figure 1, that, as the cable length increases, the speed at which the information is transmitted must be lowered in order to keep the bit error rate down. Therefore, it is very important to choose the correct standard covering the required communication distance and the needed data rate. Once the choice of standard has been made, the selection of the device required for the specific application can begin. This is not an easy task.

FireWire and GeoPort are trademarks of Apple Computer, Inc.

The matrix on the following page has been generated to give a more accurate overview of the different kind of transmission types, the modes, standards, distances, data rates, its benefits, and which TI family would suit which purpose. For every family, Texas Instruments has created a section within this application report describing the characteristics of the standard, whether or not there is a software overhead. There is, of course, also a family-dedicated web page, which contains further information on product datasheets, additional application reports, and the possibility of sampling devices via the Internet. The family link is also listed in the matrix.

Table 1. Bus Interface Selection Guide

| TYPE                                     | TRANSMISSION<br>MODE | DATA RATE<br>PER LINE | DATA RATE<br>PER DEVICE  | DISTANCE         | STANDARD                                                       | PRODUCT<br>FAMILY                 | WEB PAGE<br>http://www/ti/com/sc          |

|------------------------------------------|----------------------|-----------------------|--------------------------|------------------|----------------------------------------------------------------|-----------------------------------|-------------------------------------------|

|                                          |                      | 25/50 Mbps            |                          | 1.5 m            | IEEE1394-1995                                                  | IEEE1394<br>Backplane             | /4204                                     |

|                                          |                      | 100 – 400 Mbps        |                          | 4.5 m            | IEEE1394-1995/<br>P1394.a                                      | IEEE1394 Cable                    | <u>/1394</u>                              |

|                                          | Multipoint           | 12 Mbps               |                          | 5 m              | USB 1.1                                                        | USB                               | <u>/usb</u>                               |

|                                          |                      | 35 Mbps               |                          | 10 m<br>(1200 m) | TIA/EIA 485<br>(ISO8482)                                       | TIAEIA 485                        | /docs/products/msp/<br>datatran/index.htm |

| Serial                                   |                      | 200 Mbps              |                          | 0.5 m            | In definition                                                  | LVDM                              | <u>datatran/index.ntm</u>                 |

|                                          |                      | 10 MBps               |                          | 10 m<br>(1200 m) | TIA/EIA 422<br>(ITU-T V.11)                                    | TIA/EIA-422                       | /do on/o rodu oto/oon/                    |

|                                          | Multidrop            | 200/100 Mbps          | 4 ch: 800/<br>400 Mbps   | 0.5 m/10 m       | TIA/EIA-644/<br>TIA/EIA-644<br>(LVDS)<br>/in definition        | LVDS/LVDM                         | docs/products/msp/<br>datatran/index.htm  |

|                                          | Point-to-point       | 512 Kbps              |                          | 20 m             | TIA/EIA-232<br>(ITU-T V.28)                                    | TIA/EIA-232                       | /docs/products/msp/<br>datatran/index.htm |

| Serial                                   | Point-to-point       | 400/200 Mbps          | 4 ch: 1600/<br>800 Mbps  | 1 m/ 10 m        | TIA/EIA-644/<br>TIA/EIA-644<br>(LVDS)                          | LVDS                              | /docs/products/msp/<br>datatran/index.htm |

|                                          |                      | 455 Mbps              | 4 ch: 1.83 Gbps          | < 10 m           | TIA/EIA-644/<br>TIA/EIA-644<br>(LVDS)                          | LVDS<br>SerDes/FlatLink           | /serdes                                   |

| Parallel-to-serial<br>Serial-to-parallel | Point-to-point       | 1.25 Gbps             | 1.25 Gpbs<br>full duplex | < 10 m           | IEEE P802.3z                                                   | Gigabit Ethernet                  |                                           |

|                                          |                      | 2.5 Gbps              | 2.5 Gbps<br>full duplex  | < 10 m           | IEEE P802.3z<br>extended 2 Gbps                                | Serial Gigabit<br>CMOS            |                                           |

|                                          |                      | 35 Mbps               |                          | 10 m<br>(1200 m) | TIA/EIA-485<br>(ISO8482)                                       | TIA/EIA-485                       | /docs/products/msp/<br>datatran/index.htm |

|                                          |                      | 40/20 MHz             | 9 ch: 360/<br>180 Mbps   | 12 m/25 m        | SCSI<br>(ISO/IEC9316)                                          | SCSI                              |                                           |

|                                          |                      | 40 Mbps               | 9 ch: 360 Mbps           | 12 m             | LVD-SCSI<br>(1142-D SPI-2)                                     | LVD-SCSI                          |                                           |

|                                          |                      | 200 s/100 Mbps        |                          | 0.5 m/10 m       | In definition                                                  | LVDM                              |                                           |

|                                          |                      | 33/66 MHz             |                          | 0.2 m            | PCI Compact                                                    | PCI                               | /n oi                                     |

|                                          |                      | 33/66 MHz             |                          | 0.2 m            | PCI                                                            | PCI                               | <u>/pci</u>                               |

|                                          |                      | 4 MHz CLK             | 16 ch: 64 Mbps           | 10 m             | IEEE Std<br>1284-1994                                          | AC1284,<br>LVC161284,<br>LV161284 | <u>/logic</u>                             |

| Parallel                                 | Multipoint           | 20 MHz CLK            | 32 ch: 640 Mbps          | 0.5 m            | CMOS, JESD20,<br>TTL<br>IEEE 1014-1987                         | AC, AHC, ABT                      | /logic                                    |

|                                          |                      | 33 MHz CLK            | 20 ch: 660 Mbps          | 0.5 m            | LVTTL as stated<br>in JEDS8-A, June<br>1994,<br>IEEE 1014-1987 | LVTH, ALVT                        | /alvt<br>/lvt                             |

|                                          |                      | 40 MHz CLK            | 16 ch: 640 Mbps          | 0.5 m            | VME64 Standard<br>ANSI/VITA1-1991                              | ABTE                              | /logic                                    |

|                                          |                      | 60 MHz CLK            | 16 ch: 960 Mbps          | 0.5 m            | IEEE Std<br>1194.1-1991                                        | BTL/FB+                           |                                           |

|                                          |                      | 60 MHz CLK            | 18 ch: 1.08 Gbps         | 0.5 m            | JESD8-3                                                        | GTL/GTL+                          | <u>/gtl</u>                               |

|                                          |                      | 100 MHz CLK           | 18 ch: 1.8 Gbps          | 0.5 m            | JESD8-3                                                        | GTLP                              | /gflp                                     |

|                                          |                      | 200 MHz CLK           | 18 ch: 3.6 Gbps          | 0.1 m            | EIA/JESD8-8,<br>EIA/JESD8-9                                    | SSTL                              | <u>/logic</u>                             |

## Single-Ended Versus Differential Data Transmission

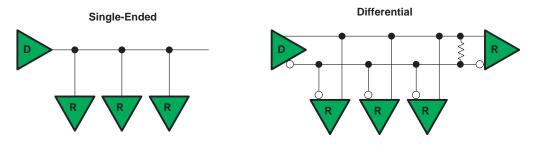

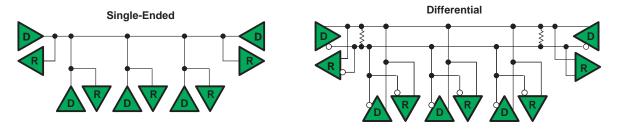

Moving on to the electrical standards, they are currently two main configurations, single-ended (or unbalanced) and differential (or balanced data transmission). The difference between single-ended and differential transmissions is essentially described below.

## Single-Ended Transmission

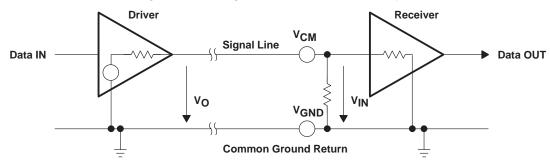

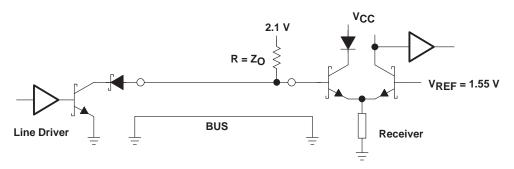

Single-ended transmission is performed on one signal line, and the logical state is interpreted with respect to ground. For simple, low-speed interfaces, a common ground return path is sufficient; for more advanced interfaces featuring higher speeds and heavier loads, a single return path for each signaling line (twisted pair cable) is recommended. Figure 2 shows the electrical schematic diagram of a single-ended transmission system.

Figure 2. Single-Ended Transmission With Parallel Termination at Line End

# **Advantages of Single-Ended Transmission**

The advantages of single-ended transmission are simplicity and low cost of implementation. A single-ended system requires only one line per signal. It is therefore ideal for cabling, and connector costs are more important than the data transfer rate, e.g. PC, parallel printer port or serial communication with many handshaking lines, e.g. EIA-232. Cabling costs can be kept to a minimum with short distance communication, depending on data throughput, requiring no more than a low cost ribbon cable. For longer distances and/or noisy environments, shielding and additional ground lines are essential. Twisted pair cables are recommended for line lengths of more than 1 meter.

## **Disadvantages of Single-Ended Transmission**

The main disadvantage of the single-ended solution is its poor noise immunity. Because the ground wire forms part of the system, transient voltages or shifts in voltage potential may be induced (from nearby high frequency logic or high current power circuits), leading to signal degradation. This may lead to false receiver triggering. For example, a shift in the ground potential at the receiver end of the system can lead to an apparent change in the signal, sufficient to drive the input across the thresholds of the receiver, thus increasing its susceptibility to electromagnetic fields.

Crosstalk is also a major concern especially at high frequencies. Crosstalk is generated from both capacitive and inductive coupling between signal lines. Capacitive coupling tends to be more severe at higher signal frequencies as capacitive reactance decreases. The impedance and termination of the coupled line determines whether the electric or the magnetic coupling is dominant. If the impedance of the line is high, the capacitive pickup is large. Alternatively, if the line impedance is low, the series impedance as seen by the induced voltage is low, allowing large induced currents to flow. Single-ended transmission is much more susceptible to external noise and the radiation of EMI is increased compared to differential systems.

These problems will normally limit the distance and speed of reliable operation for a single-ended link.

## **Differential Transmission**

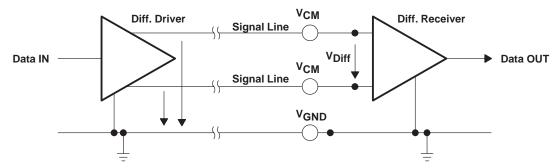

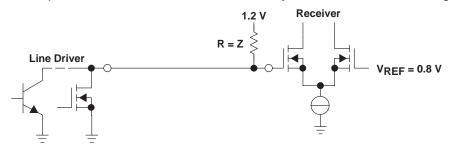

For balanced or differential transmission, a pair of signal lines is necessary for each channel. On one line, a true signal is transmitted, while on the second one, the inverted signal is transmitted. The receiver detects voltage difference between the inputs and switches the output depending on which input line is more positive. As shown in Figure 3, there is additionally a ground return path.

Figure 3. Differential Transmission

Balanced interface circuits consist of a generator with differential outputs and a receiver with differential inputs. Better noise performance stems from the fact that noise is coupled into both wires of the signal pair in much the same way and is common to both signals. Due to the common mode rejection capability of a differential amplifier, this noise will be rejected. Additionally, since the signal line emits the opposite signal like the adjacent signal return line, the emissions cancel each other. This is true in any case for crosstalk from and to neighboring signal lines. It is also true for noise from other sources as long as the common mode voltage does not go beyond the common mode range of the receiver. Since ground noise is also common to both signals, the receiver rejects this noise as well. The twisted pair cable used in these interfaces in combination with a correct line termination—to avoid line reflections—allows very high data rates of more than 10 Mbps and a cable length of up to 1200 m. Most recent standards allow up to 2.5 Gbps.

## **Advantages of Differential Transmission**

Differential data transmission schemes are less susceptible to common-mode noise than single-ended schemes. Because this kind of transmission uses two wires with opposite current and voltage swings compared to only one wire for single-ended, any external noise is coupled onto the two wires as a common mode voltage and is rejected by the receivers. This two-wire approach with opposite current and voltage swings also radiates less electro-magnetic interference (EMI) noise than single-ended signals due to the canceling of magnetic fields.

### Disadvantages of Differential Transmission

Great efforts have been made to further reduce the costs of these complex devices by developing them in a CMOS process, or to improve performance by using LinBiCMOS processes as for example for LVDS (further information on process technologies can be found at http:\\www.ti.com). Furthermore, the high data-rates that are possible with differential transmission require a very well-defined line impedance and correct line termination to avoid line reflections. For this method of transmission twisted pair cables instead of less expensive multi-conductor cables are recommended.

## **Standard Switching Levels**

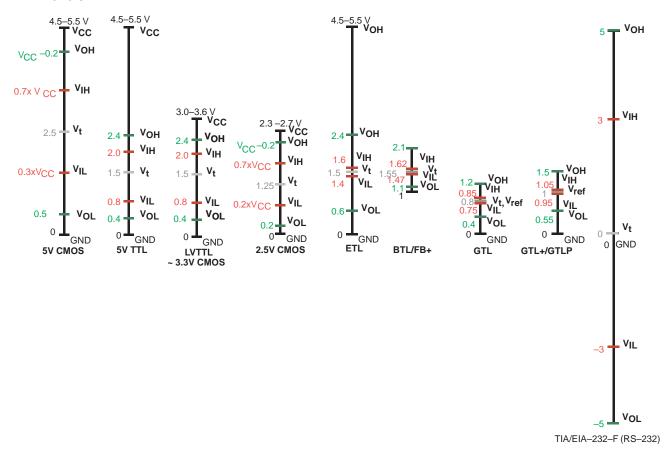

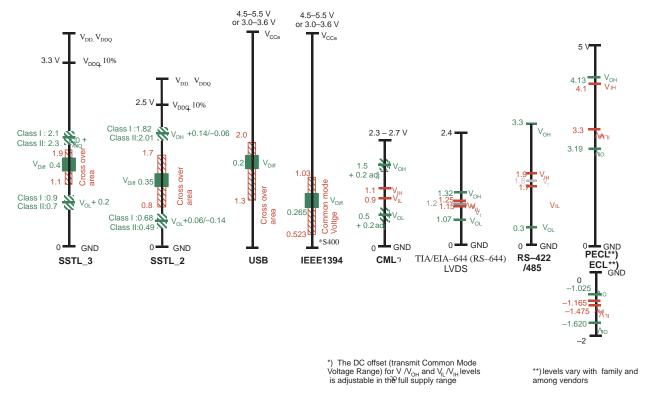

All standards are defined through input and output switching levels. Some of these levels are defined by the Joint Electron Device Engineering Council, otherwise known as JEDEC, and others are specified in the corresponding standard. Figure 4 shows the single-ended switching levels.

Figure 4. Switching Levels of Single-Ended Transmission Standards

The other set of switching levels applies to the differential or balanced technologies and are shown in Figure 5.

Figure 5. Switching Levels of Differential Transmission Standards

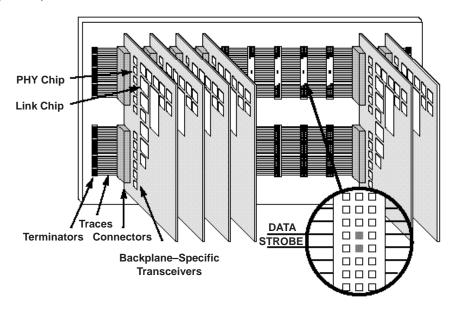

## Interconnectivity

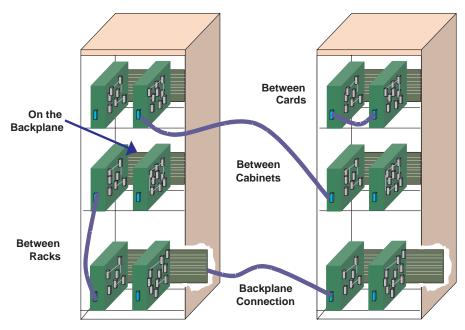

Within a data transmission system, there are numerous ways of connecting the transmitters, receivers, boards, and backplanes. Figure 6 shows how in a typical backplane rack, the cards can be linked up. The backplane itself consists of a parallel bus type configuration with each card slotted onto that bus via a connector. In some situations, it is necessary to connect either individual cards together, or a backplane to a card, etc. It would be very inconvenient to connect these devices together via a parallel cable. Serial techniques supporting a very high data rate cope with this kind of need.

Figure 6. Different Interconnection Scenarios

LVDS is one of the latest standards that has been developed for high-speed point-to-point serial transmission. What are the benefits of serial transmission compared to parallel transmission? The next section explains the principle behind the two different techniques and outlines the benefits and shortcomings of both of them.

## **Parallel Versus Serial Transmission**

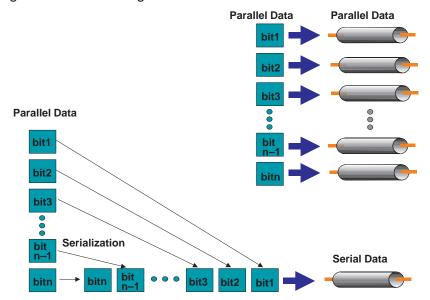

In order to understand the principle of parallel and serial transmission, Figure 7 explains in simple terms the difference between the two. In a purely parallel situation, such as a typical telecom backplane, the driver attached to the bus places n-bits of data in parallel onto the bus and all the information is sent at the same time along the backplane.

In the case of serial transmission, the data must first be converted to a serial stream. This is called the serialization. The serial data is then transmitted at high speed along the line to the receiver, which must then deserialize the information back into the original parallel data. In order for the serial technique to achieve the same data rates as the parallel one, the data must be sent along the line at a much higher speed than on the parallel bus. However, both methods have their advantages and disadvantages.

Figure 7. Principle of Parallel and Serial Transmission

## **Advantages of Parallel Transmission**

- Parallel busses do not necessarily have the time delay required by serial busses to accumulate and decode a whole bock of data. Single lines can be configured for controlling purposes, enabling a faster reaction time.

- Many industrial and telecom applications already use parallel backplanes. This means that

many designers and engineers are familiar with these kinds of systems and have the

knowledge and the experience to quickly implement such systems.

#### **Advantages of Serial Transmission**

- Fewer or no problems with line-to-line signal skew

- Serial data offers a more flexible approach to data rates allowing longer cable lengths and cheaper cable costs.

- Reduction in the number of signal lines and GND lines required to transmit the data from one point to another

- Major savings on board space

## **Various Widely Used Data Transmission Topologies**

There are currently many different methods or topologies to transmit data across wires. In this report, three main ones will be highlighted and briefly explained.

We have split this page into two columns, the left column shows the single-ended solution and the differential solution is shown in the right column. To start, we will take point-to-point connection, the principle setup for the single-ended and differential solution is shown in Figure 8.

**Point-to-Point:** This configuration is implemented with one transmitter and one receiver per line.

Figure 8. Point-to-Point Connection

**Multi-Drop:** This configuration is implemented with one transmitter and many receivers per line.

Figure 9. Multi-Drop Connection

Figure 9 shows a topology with only one driver and many receivers.

The next topology is when many receivers and transmitters connect to the same line. In this case, it is called a multi-point configuration.

**Multi-Point:** This configuration is implemented with many transmitters and many receivers per line. In practice, this solution is normally realized with a transmitter—receiver pair called a transceiver. Not all of the participants have to be transceivers. Any combination of receivers, transmitters and transceivers, is possible for this topology.

Figure 10. Multi-Point Connection Using Multiple Transceiver

## **IEEE 1394 Cable and Backplane Applications (FireWire)**

1394–1995 is an IEEE designation for a high performance serial bus. This serial bus defines both a backplane (for example, VME, FB+) physical layer and a point-to-point cable-connected virtual bus. The backplane version operates at 12.5, 25, or 50 Mbps, whereas the cable version supports data rates of 100, 200, and 400 Mbps. Both versions are compatible at the link layer and above. The interface standard defines the transmission method, media in the cable version, and protocol.

The primary application of the cable version is the interconnection of digital A/V equipment and integration of I/O connectivity at the back panel of personal computers using a low-cost, scalable, high-speed serial interface. The 1394 standard also provides new services such as realtime I/O and live connect/disconnect capability for external devices.

#### Electrical

The 1394 standard is a transaction-based packet technology for cable- or backplane-based environments. Both chassis and peripheral devices can use this technology. The 1394 serial bus is organized as if it were memory space interconnected between devices, or as if devices resided in slots on the main backplane. Device addressing is 64 bits wide, partitioned as 10 bits for bus ID, 6 bits for node ID and 48 bits for memory addresses. The result is the capability to address up to 1023 buses, with each having up to 63 nodes, each with 281 terabytes of memory. Memory-based addressing, rather than channel addressing, views resources as registers or memory that can be accessed with processor-to-memory transactions. Each bus entity is termed a unit, to be individually addressed, reset, and identified. Multiple nodes may physically reside in a single module, and multiple ports may reside in a single node.

Some key features of the 1394 topology are multi-master capabilities, live connect/disconnect (hot plugging) capability, genderless cabling connectors on interconnect cabling, and dynamic node address allocation as nodes are added to the bus. Another feature is that transmission speed is scalable from approximately 100 Mbps to 400 Mbps.

Each node acts as a repeater, allowing nodes to be chained together to form a tree topology. Due to the high speed of 1394, the distance between each node or hop should not exceed 4.5 m plus the maximum number of hops in a chain which is 16, for a total maximum end-to-end distance of 72 m. Cable distance between each node is limited primarily by signal attenuation. An inexpensive cable with 28-gauge signal pairs can be up to 4.5 meters long. The most widely separated nodes must have 16 or fewer cable hops between them. This gives an end-to-end distance of 72 meter.

A maximum of 63 nodes can be connected to one network. The cable environment uses a twisted three-pair shielded cable and a miniature connector to carry transmit/receive data as well as to source or sink power (between 8 and 40  $V_{CC}$  at no more than 1.5 A). A unique feature of the 1394 cable version is the distribution of power through the cable for operation of the transceiver's repeating functions even if the node's power is off.

The cable-based physical interface uses dc-level line states for signaling during initialization and arbitration. Both environments use dominant mode addresses for arbitration. The backplane environment does not have the initialization requirements of the cable environment because it is a physical bus and does not contain repeaters. Due to the differences, a backplane-to-cable bridge is required to connect these two environments.

The signals transmitted on both the cable and backplane environments are NRZ with data-strobe (DS) encoding. DS encoding allows only one of the two signal lines to change each data bit period, essentially doubling the jitter tolerance with very little additional circuitry overhead in the hardware.

#### **Protocol**

Both asynchronous and isochronous data transfers are supported. The asynchronous format transfers data and transaction layer information to an explicit address. The isochronous format broadcasts data based on channel numbers rather than specific addressing. Isochronous packets are issued on the average of each 125  $\mu$ s in support of time-sensitive applications. Providing both asynchronous and isochronous formats on the same interface allows both non-real-time and real-time critical applications on the same bus.

The cable environment's tree topology is resolved during a sequence of events triggered each time a new node is added or removed from the network. This sequence starts with a bus reset phase, where previous information about a topology is cleared. The tree ID sequence determines the actual tree structure, and a root node is dynamically assigned, or it is possible to force a particular node to become the root. After the tree is formed, a self-ID phase allows each node on the network to identify itself to all other nodes. During the self-ID process, each node is assigned an address. After all of the information has been gathered on each node, the bus goes into an idle state waiting for the beginning of the standard arbitration process.

An additional feature is the ability of transactions at different speeds to occur on a single device medium (for example, some devices can communicate at 100 Mbps while others communicate at 200 Mbps or 400 Mbps). Use of multispeed transactions on a single 1394 serial bus requires consideration of each node's maximum capabilities when laying out the connections to ensure that the path between two higher-speed nodes is not restricted by a device with lower-rate capabilities.

The backplane physical layer shares some commonality with the cable physical layer. Common functions include: bus state determination, bus access protocols, encoding and decoding functions, and synchronization of received data to a local clock.

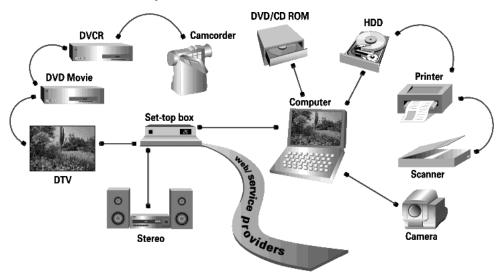

## **Applicability and Typical Application for IEEE 1394**

The transmission of data without burdening the host unit creates a huge market for IEEE1394. Not only does the computer-based equipment in private households require an interface solution for the home and home office network, but also the evolving markets of digital broadcasts, interactive services, games, and home shopping requires a high speed network. The introduction of digital set top boxes, which enable the reception of these services, enables the capability to transmit digital data not only to consumer devices like digital TV, but also to PC and storage media. Beside the consumer, PC, and PC peripheral markets, many industrial applications can be covered by IEEE1394.

Figure 11. Possible Interconnections Using 1394 as Interface

## Applicability and Typical Application for IEEE 1394 Backplane

The 1394 backplane serial bus (BPSB) plays a supportive role in backplane systems, specifically GTLP, Futurebus+™, VME64, and proprietary backplane bus systems. This supportive role can be grouped into three categories:

- Diagnostics: Alternate control path to the parallel backplane bus; test, maintenance and troubleshooting; software debug and support interface.

- System enhancement: Fault tolerance; live insertion; CSR access; auxiliary bus to the parallel backplane bus

- Peripheral monitoring: Monitoring of peripherals (disk drives, fans, power supplies, etc. in conjunction with 1394 cable serial bus.

The TSB14C01A and SN74GTLP1394 provide a way to add high-speed 1394 connections to almost any backplane.

Figure 12. Principle Application Setup Using 1394 Interface

### **Features**

- Real-time data transfer for multimedia applications

- 100, 200, and 400 Mbps data rates for high speed applications in cable environments

- 25 and 50 Mbps data rates for backplane environments

- Live connection/disconnection without data loss or interruption

- Automatic configuration supporting plug and play

- Free network topology allowing branching and daisy-chaining

- Guaranteed bandwidth assignments for real-time applications

Table 2. Top IEEE 1394 Link Layer Device List (PC)

| DEVICE                | SPEED    | POWER                 | PACKAGE      |

|-----------------------|----------|-----------------------|--------------|

| OHCI-Lynx – TSB12LV23 | 400 Mbps | 3.3 V (5-V tolerance) | 100-pin TQFP |

| PCILynx2 – TSB12LV21B | 400 Mbps | 3.3 V (5-V tolerance) | 176-pin TQFP |

### Table 3. Top IEEE 1394 Link Layer Device List (Non-PC)

| DEVICE                | SPEED    | POWER                 | PACKAGE      |

|-----------------------|----------|-----------------------|--------------|

| MPEGLynx - TSB12LV41A | 200 Mbps | 3.3 V (5-V tolerance) | 100-pin TQFP |

| DVLynx – TSB12LV42    | 200 Mbps | 3.3 V (5-V tolerance) | 100-pin TQFP |

| TSB12LV01A            | 400 Mbps | 3.3 V (5-V tolerance) | 100-pin TQFP |

| GP2Lynx – TSB12LV32   | 400 Mbps | 3.3 V (5-V tolerance) | 100-pin TQFP |

Table 4. Top IEEE 1394 Physical Layer Device List

| DEVICE                | PORTS | SPEED    | POWER                 | PACKAGE      |

|-----------------------|-------|----------|-----------------------|--------------|

| TSB41LV02             | 2     | 400 Mbps | 3.3 V (5-V tolerance) | 64-pin TQFP  |

| TSB41LV03/04          | 3/4   | 400 Mbps | 3.3 V (5-V tolerance) | 80-pin TQFP  |

| TSB41LV06             | 6     | 400 Mbps | 3.3 V (5-V tolerance) | 100-pin TQFP |

| TSB14C01A (Backplane) | Х     | 100 Mbps | 5-V                   | 68-pin TQFP  |

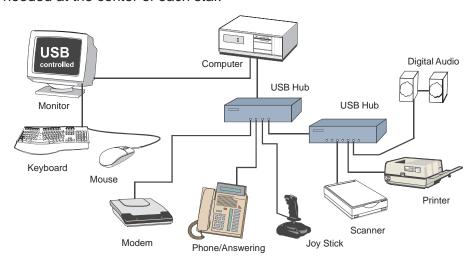

## **Universal Serial Bus (USB)**

Flexibility, expandability, and ease of use are all important in meeting the needs of the growing numbers of PC users. Until now, the traditional PC's peripheral expansion capabilities have largely limited these important user concerns. The new USB standard is an important tool that gives a simple way to expand a system in a virtually unlimited number of ways. Most important, this functionality is available today.

USB is designed to simplify a user's effort by combining the PC's many existing interfaces, like the TIA/EIA-232C serial ports, parallel port, game/MIDI port and more, into a single, easy-to-use connector. In itself, this capability greatly reduces the complexity of the system and gives manufacturers the ability to develop highly integrated products. USB's true plug-and-play capability also signals an end to the often complex process of adding system peripherals.

#### **Electrical**

The USB physical interconnect is a tiered star topology. A hub is at the center of each star. Each wire segment is a point-to-point connection between the host and a hub or function, or a hub connected to another hub or function. The USB transfers signal and power over a four-wire cable. The signaling occurs over two wires on each point-to-point segment.

There are two data rates: full-speed signaling bit rate at 12 Mbps and a limited capability low-speed signaling mode at 1.5 Mbps. Both modes can be supported in the same USB bus by automatic dynamic mode switching between transfers. The low-speed mode is defined to support a limited number of low-bandwidth devices, such as a mouse, because more general use would degrade bus utilization. The clock is transmitted, encoded along with the differential data. The clock encoding scheme is NRZI with bit stuffing to ensure adequate transitions. A SYNC field precedes each packet to allow the receiver(s) to synchronize their bit recovery clocks. The cable also carries VBUS and GND wires on each segment to deliver 5 V power to devices.

#### **Protocol**

The USB is a polled bus. The host controller initiates all data transfers.

All bus transactions involve the transmission of up to three packets. Each transaction begins when the host controller, on a scheduled basis, sends a USB packet describing the type and direction of transaction, the USB device address, and endpoint number. This packet is referred to as the token packet. The addressed USB device selects itself by decoding the appropriate address fields. In a given transaction, data is transferred either from the host to a device or from a device to the host. The direction of data transfer is specified in the token packet. The source of the transaction then sends a data packet or indicates it has no data to transfer. The destination, in general, responds with a handshake packet indicating whether the transfer was successful.

The USB data transfer model between a source or destination on the host and an endpoint on a device is referred to as a pipe. There are two types of pipes: stream and message. Stream data has no USB-defined structure, while message data does. Additionally, pipes have associations of data bandwidth, transfer service type, and endpoint characteristics like directionality and buffer sizes. Most pipes come into existence when a USB device is configured. One message pipe, the default control pipe, always exists once a device is powered, in order to provide access to the device's configuration, status, and control information.

The transaction schedule allows flow control for some stream pipes. At the hardware level, this prevents buffers from underrun or overrun situations by using a negative acknowledgment handshake to decrease the data rate. When negative acknowledged, a transaction is retried when bus time is available. The flow control mechanism permits the construction of flexible schedules that accommodate concurrent servicing of a heterogeneous mix of stream pipes. Thus, multiple stream pipes can be serviced at different intervals and with packets of different sizes.

## **Applicability and Typical Applications**

USB is a PC-centric system designed to interconnect up to 127 peripherals to the PC including the ones pictured below: keyboard, mouse, printer, modem, etc. Due to the tiered star topology, a hub is needed at the center of each star.

Figure 13. USB – Tiered Star Topology

- Single PC supports up to 127 devices

- Data rates of 1.5 Mbps and 12 Mbps supported

- Ends confusion of multiple add-in cards for ease of use

- Universal connectors and cables for all devices and applications

- Auto configuration upon connection for real plug and play

- Guaranteed bandwidth for real-time applications

Table 5. Top USB HUB Device List

| DEVICE          | DOWNSTREAM PORTS | POWER | PACKAGE                   |

|-----------------|------------------|-------|---------------------------|

| TUSB2046/43     | 4                | 3.3 V | 32-pin LQFP               |

| TUSB2077        | 7                | 3.3 V | 48-pin LQFP               |

| TUSB2140B + I2C | 4                | 3.3 V | 40-pin DIP or 44-pin TQFP |

### TIA/EIA-232

RS is the abbreviation for recommended standard. Usually, it is based on or is identical to other standards, e.g., EIA/TIA-232-F. The following section gives a closer view of these specifications, their benefits, and applicability. Where appropriate, the protocol is briefly described.

TIA/EIA-232, previously known as RS-232 was developed in the 1960's to interconnect layers of the interface (ITU-T V.11), but also the pignut of the appropriate connectors (25-pin D-type or 9-pin DB9S) (ISO 2210) and the protocol (ISSUED-T V.24). The interface standard specifies also handshake and control lines in addition to the 2 unidirectional receive data line (RD) and transmit data line (TD). The control lines data carrier detect (DCD), data set ready (DSR), request to send (RTS), clear to send (CTS), data terminal ready (DTR), and the ring indicator (RI) might be used, but do not necessarily have to be (for example, the PC-serial-mouse utilizes only RI, TD, RD and GND). Although the standard supports only low speed data rates and line length of approximately 20 m maximum, it is still widely used. This is due to its simplicity and low cost.

#### **Electrical**

TIA/EIA-232 has high signal amplitudes of  $\pm$ (5 V to 15 V) at the driver output. The triggering of the receiver depends on the sign of the input voltage: that is, it senses whether the input is above 3 V or less than -3 V. The line length is limited by the allowable capacitive load of less than 2500 pF. This results in a line length of approximately 20 m. The maximum slope of the signal is limited to 30 V/ $\mu$ s. The intention here is to limit any reflections that can occur to the riseand fall-times of the signal. Therefore, transmission line theory does not need to be applied, so no impedance matching and termination measures are necessary. Due to the voltage swings of -5...15 to 5...15 V a dual supply voltage was necessary in the past. Nowadays many devices operate with single supplies, generating the large positive and negative driver output voltage swings with integrated charge-pumps.

### **Protocol**

Different from other purely electrical-layer-standards, TIA/EIA-232 defines not only the physical layer of the interface (ITU-T V.11), but also the pinout of the appropriate connectors (25-pin D-type or 9-pin DB9S) (ISO 2210) and the protocol (ITU-T V.24). The interface standard specifies also handshake and control lines in addition to the 2 unidirectional receive data line (RD) and transmit data line (TD). The control lines might be used, but do not necessarily have to be.

## **Applicability**

TIA/EIA-232 is historically associated with computers interfacing with peripherals at low speed, short distance, for example, mouse, modem, joystick, etc., or to interconnect two PCs (that is, null modem, Figure 14). Today other equipment also uses TIA/EIA-232 I/O, for example, for programming purposes.

Figure 14. Null Modem Application Using RS232

- Established standard

- Inexpensive

- Universally used

Table 6. Top TIA/EIA-232 Device List

| DEVICE     | BIT WIDTH   | POWER                                  | ESD PROTECTION | PACKAGE           |

|------------|-------------|----------------------------------------|----------------|-------------------|

| SN74LP1185 | 3 drivers/  | V <sub>CC</sub> : 5 V, 12 V, and –12 V | ±15 kV HBM ESD | 20-pin PDIP, SOIC |

|            | 5 receivers | I/O: LVTTL/.RS-232                     | (on bus pins)  | SSOP, and TSSOP   |

| SN85LPE185 | 3 drivers/  | V <sub>CC</sub> : 5 V, 12 V, and –12 V | ±15 kV HBM ESD | 20-pin PDIP, SOIC |

|            | 5 receivers | I/O: LVTTL/.RS-232                     | (on bus pins)  | SSOP, and TSSOP   |

| SN75LP196  | 5 drivers/  | V <sub>CC</sub> : 5 V, 12 V, and –12 V | ±15 kV HBM ESD | 20-pin PDIP, SOIC |

|            | 3 receivers | I/O: LVTTL/.RS-232                     | (on bus pins)  | SSOP, and TSSOP   |

### **TIA/EIA-422**

TIA/EIA-422 (RS-422) allows a multi-drop interconnection of one driver, transmitting unidirectionally to up to 10 receivers. Although it is not capable of bidirectional transfer, it is still applicable and used for talker-audience scenarios.

#### **Electrical**

TIA/EIA-422 (ITU-T V.11) is comparable to TIA/EIA-485. It is limited to unidirectional data traffic and is terminated only at the line-end opposite to the driver (please refer to the multi-drop-explanation at the beginning of this report). The maximum line length is 1200m, the maximum data rate is determined by the signal rise- and fall-times at the receiver's side (requirement: <10% of bit duration) and ends up to be approximately 10 Mbps. TIA/EIA-422 allows up to ten receivers (input impedance of 4 k $\Omega$  attached to one driver. The maximum load is limited to 80  $\Omega$ . Although any TIA/EIA-485 transceiver can be used in a TIA/EIA-422 system, dedicated TIA/EIA-422 circuits are not feasible for TIA/EIA-485, due to short circuit current limitations. The TIA/EIA-422 standard requires only short circuit limitation to 150 mA to ground, while TIA/EIA-485 additionally has to limit short circuit currents to 250 mA from the bus pins to -7 V and 12 V to address malfunctions in combination with ground shifts.

#### **Protocol**

Not applicable/none specified

## **Applicability**

TIA/EIA-422 is very often used in industrial areas due to its robustness. Compared to TIA/EIA-485, it can only control without receiving any feedback from the listeners since its transmission mode is multi-drop, meaning only one driver is attached to a bus with multiple receivers. Backplane applications are often realized with a TIA/EIA-422 physical layer.

- Established standard

- Good for multi-drop over long distances

- Good for use in noisy environments

- Wide temperature range: -40°C to 85°C suitable for industrial applications

Table 7. Top TIA/EIA-422 Device

| DEVICE     | BIT WIDTH   | POWER                                        | PACKAGE              |

|------------|-------------|----------------------------------------------|----------------------|

| AM26LS31   | 4 drivers   | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/RS-422 | 16-pin PDIP and SOIC |

| AM26LS32A  | 4 receivers | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/RS-422 | 16-pin PDIP and SOIC |

| SN75ALS192 | 4 drivers   | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/RS-422 | 16-pin PDIP and SOIC |

### TIA/EIA-485

Historically, TIA/EIA-422 was on the market before TIA/EIA-485. Due to the lack of bidirectional capabilities, a new standard adding this feature was created: TIA/EIA-485 . The standard (TIA/EIA-485-A or ISO/IEC 8284) defines the electrical characteristics of the interconnection, including driver, line, and receiver. It allows data rates in the range of 35 Mbps and above and line lengths of up to 1200 m. Of course both limits can not be reached at the same time. Furthermore, recommendations are given regarding wiring and termination. The specification does not give any advice on the connector or any protocol requirements.

#### **Electrical**

TIA/EIA-485 describes a half-duplex, differential transmission on cable lengths of up to 1200 m and at data rates of typically up to 35 Mbps (requirement similar to TIA/EIA-422, but tr<30% of the bit duration, there are also faster devices available, suited for higher rates under certain load-conditions). The standard allows a maximum of 32 unit loads of 12 k $\Omega$ , equal to 32 standard nodes or even higher count with increased input impedance. The maximum total load should not drop below 52  $\Omega$ . The common-mode voltage levels on the bus have to maintain between –7 V and 12 V. The receivers have to be capable to detect a differential input signal as low as 200 mV.

#### Protocol

Not applicable/none specified; exceptions: SCSI systems (please refer to appropriate section) and the DIN-Bus DIN66348

## **Applicability**

Due to the robustness against noise because of the differential transmission mode and to ground shifts achieved by the large common mode voltage range, this standard is perfectly suited for industrial applications. The data rate is usually sufficient, e.g., to control a process line. TIA/EIA-485 is also very widely used for backplanes (e.g., telecom applications) since the high node-count and data-integrity are necessary features for these applications.

- Very robust interface (common mode range: -7 V to 12 V) suitable for industrial applications

- Wide temperature range: -40°C to 85°C suitable for industrial applications

- Up to 64 nodes with the SN75LBC184

Table 8. Top TIA/EIA-485 Device List

| DEVICE     | BIT WIDTH | POWER                                        | PACKAGE    |

|------------|-----------|----------------------------------------------|------------|

| SN75LBC184 | 1 Ch      | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/RS-485 | 8-pin SOIC |

| SN75LBC176 | 1 Ch      | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/RS-485 | 8-pin SOIC |

| SN75ALS176 | 1 Ch      | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/RS-485 | 8-pin SOIC |

## SCSI

Small computer systems interface (SCSI) has been developed in order to interconnect computers and its peripherals with a high data throughput. The first standard described a single ended interconnection. The next generation was high voltage differential – small computer systems interface (HVD-SCSI), which uses TIA/EIA-485 as the physical layer. Low voltage differential – small computer systems interface (LVD-SCSI) standard has been evolved to address even higher data rates.

#### **Electrical**

Electrically, HVD-SCSI is identical to TIA/EIA-485 (please refer to the TIA/EIA-485 section for details). The maximum line length is reduced to 25 m at 20 Mbps or 12 m at 40 Mbps. Details can be found in the ISO/IEC 9316 Standard: *Information technology, Small Computer System Interface-2*.

Single ended SCSI operates on TTL-levels and supports data rates up to 10 Mbps. LVD-SCSI is a newer standard with electrical levels similar to TIA/EIA-644 or LVDS (please refer to the appropriate section). It supports transmission speeds up to 40 Mbps on 12 m length, but 80 Mbps and even 160 Mbps are targeted with the upcoming specifications. Furthermore, the EMI of LVD-SCSI is reduced by approximately 90% compared to single-ended SCSI and the power consumption is at about 20% of HVD-SCSI. The maximum number of nodes including the host/controller is eight. A separate control bus, consisting of nine lines, is necessary for synchronization, arbitration, and addressing purposes. Furthermore, a parity bit is added to the 8-bit data bus. Wide SCSI utilizes an additional 8 (+1 parity) bit data bus to transfer a 16 bit wide SCSI word.

#### Protocol

The SCSI protocol is also defined in the ISO/IEC 9316 Standard: *Information Technology, Small Computer System Interface-2*. All commands as well as pin assignments are specified therein. Timing and arbitration are also described. As the standard is very voluminous, it is out of the scope of this report to get into details. For further information please refer to the mentioned standard.

## **Applicability and Typical Application**

SCSI is suited for the interconnection of equipment transferring a high amount of data in a parallel mode (byte, double, 32-bit wide). Therefore, nowadays it is primarily used in the computer domain to interconnect a host (computer) with its peripherals (printer, scanner, hard disks, CD-RW, etc). Recently, manufacturers of other hardware, which requires a high data throughput, have explored the advantages of SCSI as well. The node-limit of eight is sometimes not sufficient, but the limit can be exceeded in proprietary systems.

- Established standard

- Can migrate from single-ended SCSI to HVD and then LVD

**Table 9. Top SCSI Device List**

| DEVICE      | BIT WIDTH           | POWER                                                | PACKAGE                        |

|-------------|---------------------|------------------------------------------------------|--------------------------------|

| SN75976     | 9 Ch HVD SCSI       | V <sub>CC</sub> : 5 V<br>I/O: (LV)TTL/HVD-SCSI       | 56-pin SSOP or<br>56-pin TSSOP |

| SN75LVDM976 | 9 Ch LVD or SE-SCSI | V <sub>CC</sub> : 5 V<br>I/O: (5 V) CMOS/LVD/SE-SCSI | 56-pin TSSOP                   |

# TIA/EIA-644 (LVDS)

Low voltage differential signaling (LVDS) is an approach to achieve higher data rates on commonly used media. Since the limitation of the previously known differential standards is mainly related to the maximum achievable slew rate and EMI restrictions, the new development targets low voltage swings that will be reached much faster, even while the slew rate remains the same. In this way, in addition to enabling higher speeds, EMI, as well as power assumption, is reduced.

#### **Electrical**

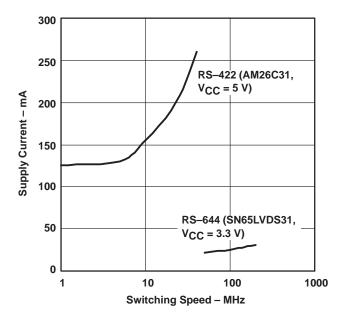

As the name says, LVDS utilizes differential transmission mode and low signal amplitudes. The swing is in the range of only 300 mV, generated on a 100  $\Omega$ -termination resistor. The driver is actually a current mode driver forcing an output current between 2.47 mA and 4.54 mA into either one of the two outputs. This way, the device is always drawing the same supply current and eliminates almost any feedback to the supply. In comparison, a voltage mode driver (like used for TIA/EIA-422) pulls much higher current during the switching period than in the steady state. The chart below shows the dependency of the supply current versus the switching frequency. As can be seen, the supply current is significantly lower and also the increase over frequency is much lower with the use of LVDS drivers.

Figure 15. Supply Current Versus Switching Frequency

The standard allows up to 655 Mbps. The maximum line length is not specified. 15 m is given as a recommendation. The specification addresses only point-to-point interfaces, but it allows the attachment of multiple receivers if attention is paid to several conditions. These include stub line length, termination, and signaling rate.

#### **Protocol**

There is no protocol specified for TIA/EIA-644. This is left to the user/hardware designer.

## **Applicability**

LVDS targets applications that transfer data point-to-point at very high speeds. It is also capable of driving multiple receivers if care is taken regarding the load configuration (that is, it can be used as a TIA/EIA-422 replacement, if certain conditions are met.) LVDS is particularly suitable for any application that requires low power and/or low EMI. The common mode input voltage, which is currently limited to 0 V to 2.4 V, restricts the usage of LVDS with long line lengths causing unpredictable ground shifts as well as the use in electrically noisy environments.

- Very high speed

- Very low power consumption

- Very low EMI

- Low cost

- Same pinout as existing TIA/EIA-422 and TIA/EIA-485 Parts

Table 10. Top LVDS Device List

| DEVICE        | BIT WIDTH | POWER                                       | PACKAGE     |

|---------------|-----------|---------------------------------------------|-------------|

| SN65LVDS31/32 |           | V <sub>CC</sub> : 3.3 V<br>I/O: LVTTL/.LVDS | 16-pin SOIC |

| SN65LVDS179   | 400 Mbps  | V <sub>CC</sub> : 3.3 V<br>I/O: LVTTL/LVDS  | 8-pin SOIC  |

#### **LVDM**

LVDM stands for LVDS-multi-point, enabling a half-duplex operation with LVDS voltage levels and speeds. It benefits from the same advantages as LVDS, additionally it allows bidirectional data transfer and the attachment of several drivers, receivers, and/or transceivers.

#### **Electrical**

LVDM is LVDS with doubled driver output current. Due to the bidirectional transfer capability, a line termination is needed at each end. The requirement of termination matching the line impedance remains. Therefore, both ends are terminated with 100  $\Omega$ . The effective termination resistance will result in the parallel configuration of these two resistors, equaling half the impedance or twice the load. To ensure the same input voltage levels like with LVDS at a 100- $\Omega$  load, the output current is doubled to generate the required amplitude on just 50  $\Omega$ .

#### **Protocol**

Not applicable/none specified.

## **Applicability**

LVDM can be used as a replacement for TIA/EIA-485 interconnections, especially for high speed, low power and/or low EMI interfaces. Like LVDS, the common mode input range is between 0 V and 2.4 V which limits the line length and the applicability in a electrically noisy environment. It is suited for backplane applications and cabled interfaces.

- Very high speed

- Very low power consumption

- Very low EMI

- Low cost

- Same pinout as existing TIA/EIA-42 and TIA/EIA-485 parts

**Table 11. Top LVDM Device List**

| DEVICE      | BIT WIDTH | POWER                                      | PACKAGE     |

|-------------|-----------|--------------------------------------------|-------------|

| SN65LVDM176 | 400 Mbps  | V <sub>CC</sub> : 3.3 V<br>I/O: LVTTL/LVDS | 8-pin SOIC  |

| SN65LVDM050 | 400 Mbps  | V <sub>CC</sub> : 3.3 V<br>I/O: LVTTL/LVDM | 16-pin SOIC |

## LVDS Serdes and FlatLink

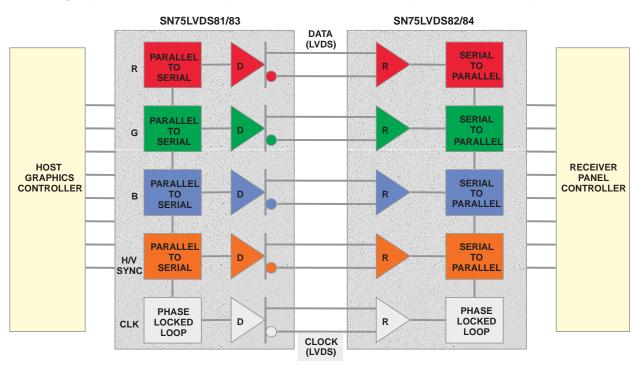

LVDS serializer deserializer (serdes) and FlatLink technology based devices physically interconnect two parallel bus systems through a high frequency serial data path using LVDS technology. The following explanations apply to both, LVDS serdes and FlatLink type devices; differences are mentioned in the text accordingly.

**Principle of a Serdes (serializer/deserializer) Device:** The requirement for functionality is a transmitter and a receiver. From a user standpoint, the application is doing nothing more than repeating a number of parallel-clocked data over a longer distance. Therefore, the receiver's output appears to the user the same as the signal seen on the transmitter's input bus. The range for the bus clock rate is limited (e.g., 31–65 MHz).

The transmitter has a certain number of LVTTL compatible data input pins (parallel bus) and a clock input. The input pins are split up into different groups. All of the data signals in one group become serialized into a higher frequent data stream and sent out over differential lines (LVDS). A typical compression value is 1:7. The process can be compared with a multiplexer which is switching between all signals of a group running on a frequency equal to the clock multiplied by the number of pins in this group. This serial data stream is sent into a differential pair of lines based on LVDS. The original clock signal is transferred over an additional pair of lines.

On the receiving side, the high frequency differential data stream is demultiplexed separately for each group (each differential input) and clocked out to the parallel LVTTL compatible output bus.

Table 12. Typical Multiplexing Ratio for Serdes Devices

| Transmitter | Input (LVTTL):<br>Output (LVDS serial link): | 21 lines + clock<br>3 lines + clock |

|-------------|----------------------------------------------|-------------------------------------|

|             | Input (LVDS serial link):<br>Output (LVTTL): | 3 lines + clock<br>21 lines + clock |

#### **Electrical**

No industrial standard covering LVDS serdes or FlatLink devices has been defined so far.

The I/O Bus pins are LVTTL compatible. The transmission is based on LVDS. All devices meet or exceed the ANSI EIA/TIA-644 Standard that specifies LVDS. LVDS serdes devices are designed for the industrial temperature range (–40°C to 85°C) running on a single 3.3 V power supply. Depending on the transmission frequency, the transmission media, and the environment (noise level), LVDS serdes supports a transfer distance of up to 16 meter.

#### **Protocol**

No protocol is specified for LVDS serdes or FlatLink; this is left to the user/hardware designer.

## **Applicability**

**FlatLink:** is designed to transfer large data packets from the CPU to the graphic LCD display in a notebook type of application. The major advantages compared with realizing this transfer based on standard bus logic are in reduced number of parallel data lines, reduced power consumption, and lower electromagnetic emission.

**LVDS Serdes:** The differential transmission mode provides high robustness against in-coupling noise. Therefore, LVDS serdes devices are perfectly suited to industrial applications, as point-to-point connection in telecom backplanes, or to interconnect two parallel bus systems.

**Bus speed:** The clock rate of those bus systems must be chosen within a defined range. The limiting factor for minimum and maximum clock speed is the PLL of the transmitter that needs to lock to the clock input. Test of devices specified for 31 MHz to 65 MHz clock input have shown that they work down as low as 10 MHz at room temperature and the highest data rate is slightly above 65 MHz.

**Bus skew:** The output data clock of the serdes receiver is a device specific parameter, independent of the input bus skew. This might help to overcome bus skew problems.

**Bus Topology:** Serdes can be used as point-to-point or multi-drop connections as well as replacing slower bus systems via a daisy chaining architecture.

**Initialization after reset/power down:** As typical in all PLL based applications, the receiver requires a certain time to lock to the clock signal. Therefore, the result on the receiver output becomes valid after a duration of 1 ms.

Figure 16. Typical Application – FlatLink Used as an Interface in a Notebook

- PLL lock range 31–65 MHz (speed for parallel input bus

- Data throughput up to 455 Mbps over each differential pair

- Industrial temp spec (-40°C to 85°C for LVDS serdes

- Very low power consumption and low emission (portable devices)

- Cost per Mb transfer rate very low (1.1 Cent)

- Very low power consumption when disabled (below 1 mW)

- Easy hardware implement of parity proof, due to high number of parallel inputs

**Table 13. Top LVDS Serdes Device List**

| DEVICE                      | Serdes Ratio | MAXIMUM<br>THROUGHPUT | V <sub>CC</sub> AND I/O                                        | PACKAGE      |

|-----------------------------|--------------|-----------------------|----------------------------------------------------------------|--------------|

| LVDS serdes                 |              |                       |                                                                |              |

| SN65LVDS93/94               | 28:4         | 1.365 Gbps            | 3.3 V<br>Parallel I/O: LVTTL<br>Serial I/O: LVDS               | 56-pin TSSOP |

| SN65LVDS95/96               | 21:3         | 1.8 Gbps              | Power supply: 3.3 V<br>Parallel I/O: LVTTL<br>Serial I/O: LVDS | 48-pin TSSOP |

| FlatLink                    |              |                       |                                                                |              |

| SN75LVDS84A/<br>SN75LVDS86A | 21:3         | 1.8 Gpbs              | 85 mW typical (84A)<br>145 mW typical (86A)                    | 48-pin TSSOP |

## **Serial Gigabit CMOS**

The product family of gigabit serdes devices has been made to bridge large number of data bits over a small number of data lines. The input to the transceiver is a parallel bus system, bit wide (n=1,2,4,8), with a clock speed in the 100 MHz range. This input bus signal will be serialized and sent over a differential pair of cable to the second transceiver which recovers (de-serializes) the bus pattern and clocks it out in parallel. Input and output bus appear identical to the user.

Serial gigabit CMOS products address primary point-to-point high-speed data transfer applications.

#### **Electrical**

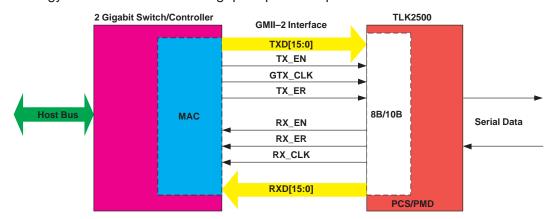

Ultra high-speed serdes devices are compliant to the IEEE802.3z gigabit ethernet standard defined by the IEEE P802.3z gigabit task force. This standard specifies the physical and the data link layer (in reference to the OSI model) for a serializer/deserializer device running up to 1 Gbps throughput. The model is split into 6 main tasks as it is logical link control (LLC), media access control (MAC), reconciliation, physical coding sublayer (PCS), physical medium attachment (PMA), and physical layer medium dependent (PMD). The definitions are made to be inline with the gigabit media independent interface (GMII) transmission standard, defining signal functions for a interface up to 1 Gbps. TI extended this standard to GMII-2 with the same terminology but effective data throughput up to 2 Gbps.

Figure 17. GMII-2 Interface

Parallel I/O side:  $V_{CC} \pm 0.3 \text{ V}$ .

**Serial (transmission) side:** The driver design on the serial side is not specified in the IEEE802.3z. Texas Instruments is using high-speed current mode logic (CML) technology. With a typical logic swing of 400 mV and input sensitivity of 200 mV this technology provides sufficient noise margin for most applications. The CML interface is chosen for:

- 1. Low power consumption

- 2. High noise immunity

- Ease of defining logic swing at the receiver

- 4. Inherently short circuit proof

- 5. Simpler level shifting to CMOS levels

- 6. Adjustable logic swing can save power over short connections

The following steps will be performed on the transmitter side:

- 1. The incoming bus signal will be buffered in reference to the input clock signal

- 2. 8B10B encoding of the data word (this ensures clock recovery on the receiver side due to a high transition rate of equal/above 3+1 transitions on 8 bit data)

- 3. Serialization of the data

- 4. Clock the serial data into the differential line using the CML driver

The receiver side performs the reverse operations in reverse order to regenerate to original sent word.

Figure 18. Serdes Interface Using Two Transceivers

**Transmission media:** The transmission media of the serial path can be PCB, copper cable, or fiber-optics using an electrical-to-optical translator circuit in-between. The impedance of the copper must be matched to 50 (75)  $\Omega$ . The maximum distance to be bridged depends on the transmission speed and the transmission media; tests showed proper functionality up to 5 m over coax cable.

### **Protocol**

There is no protocol specified for IEEE802.3z. This is left to the user/hardware designer. The upper 5 layer (application, presentation, session, transport and network) of the OSI reference model are left open to be used application-specifically.

## **Applicability**

The differential transmission mode provides high robustness against in-coupling noise. Therefore, serdes devices suit perfectly into networking, telecommunication, or data-communication designs or to interconnecting two parallel bus systems.

**Bus speed:** The clock rate of those bus systems can be chosen within a certain range (e.g., 80–125 MHz). The limiting factor on minimum and maximum clock speed is the PLL on the receiver side, which has to recover the clock out of the serial data stream.

**Bus skew:** The output data clock of a gigabit series device is device specific and independent of the input bus skew. This might help to overcome bus skew problems.

**Bus Topology:** Series can be used as point-to-point connection as well as replacing slower bus systems via a daisy chain architecture.

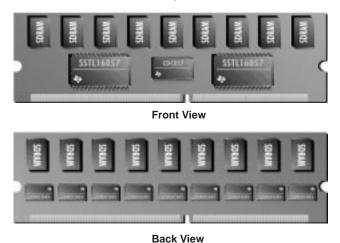

**Initialization after reset/power down:** As typical in all PLY based applications, the receiver requires a certain time to lock to the incoming serial signal. Therefore, the receiver output and control pins are kept into a high-impedance state that could take one millisecond.